# Monolithic Transformer-Coupled RF Power Amplifiers in Si-Bipolar

Werner Simbürger, Daniel Kehrer<sup>1</sup>, Alexander Heinz, Hans-Dieter Wohlmuth, Mirjana Rest, Klaus Aufinger, Arpad L. Scholtz<sup>1</sup>

> INFINEON Technologies, Corporate Research Munich, Germany

<sup>1</sup> Technical University of Vienna, Institute of Communications and Radio Frequency Engineering, Austria

# Outline

#### Introduction

- ► High Performance On-Chip Transformer Design

- ► A 2.5 V, 1 W Si-bipolar PA with 55 % PAE at 1.9 GHz

- ► A 2.8 V, 3.2 W Si-bipolar PA with 54 % PAE at 900 MHz

#### Conclusion

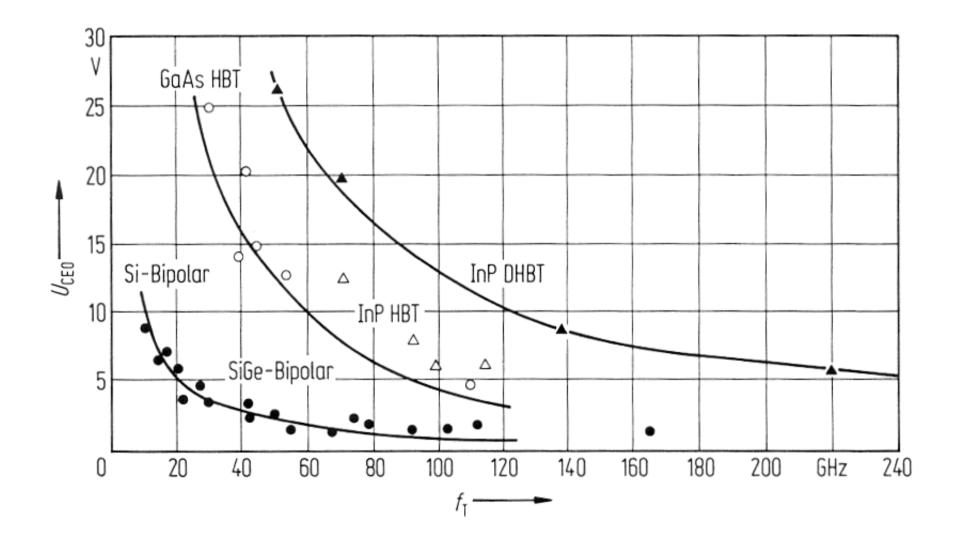

# **BV<sub>CE0</sub> versus Transit Frequency**

### **Motivation & Challenges**

- high output power at very low supply voltages, e.g.: 0.5 W, 1.8 V, 2 GHz and 3 W, 2.8 V, 900 MHz

- ▶ high efficiency > 50 %

- monolithic integration

- standard low-cost Si-bipolar technology

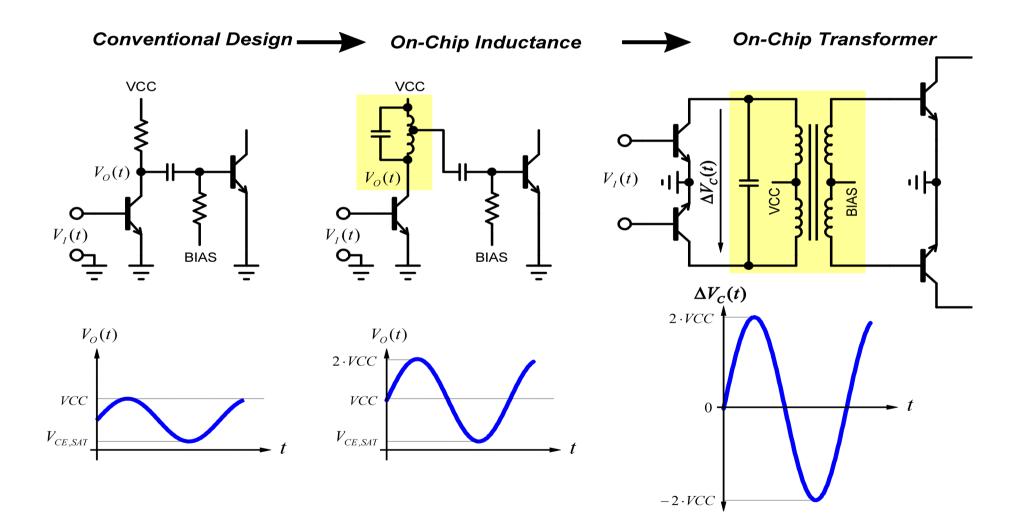

# **On-Chip Interstage Matching**

# **Push-Pull Type Power Amplifier**

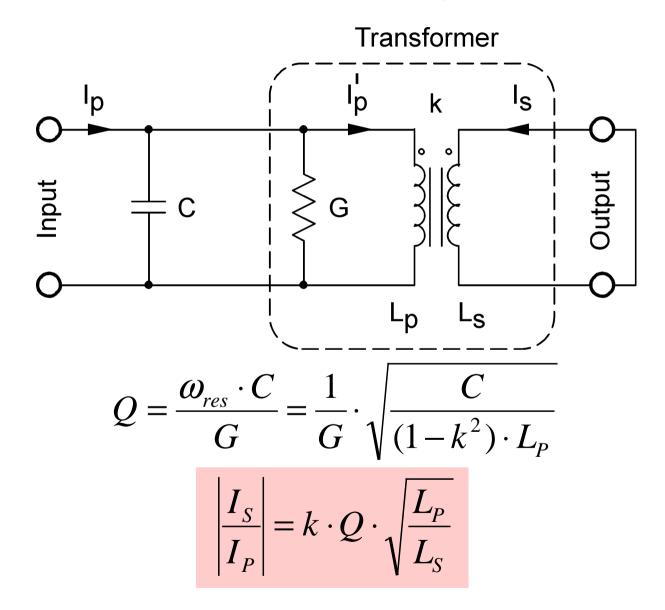

#### **Current Transfer Ratio of a Lossy Tuned Transformer**

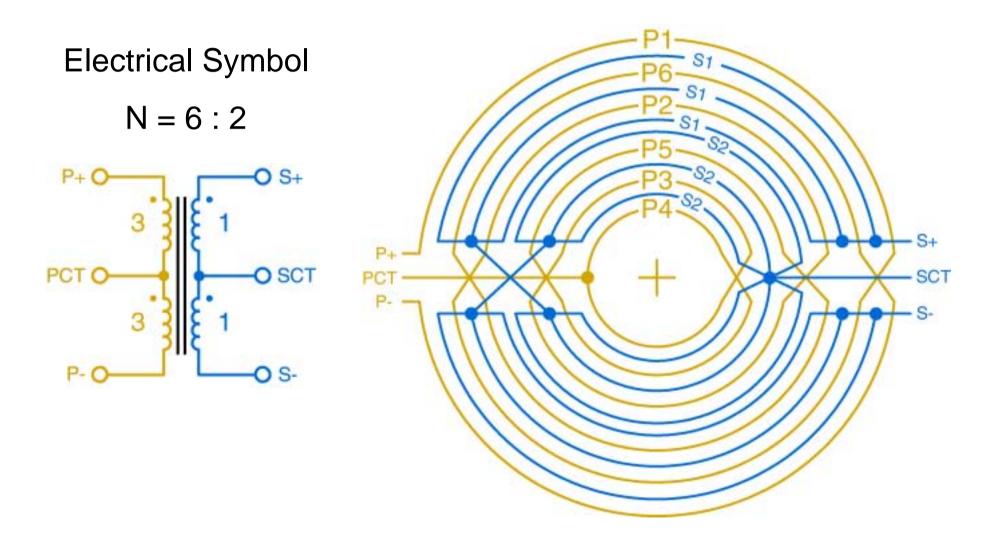

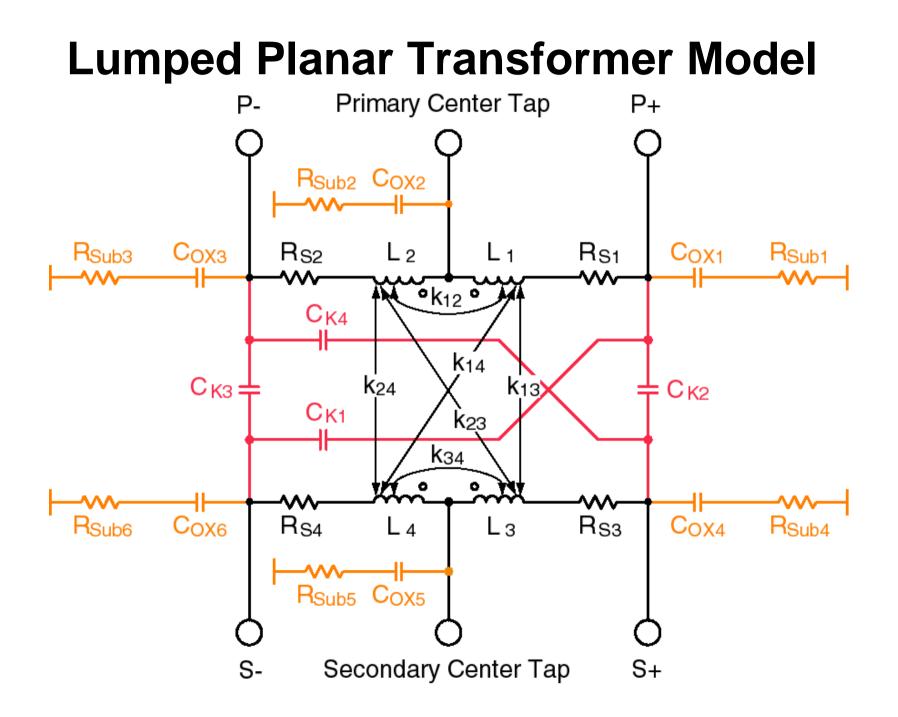

#### **Monolithic Transformer Winding Scheme**

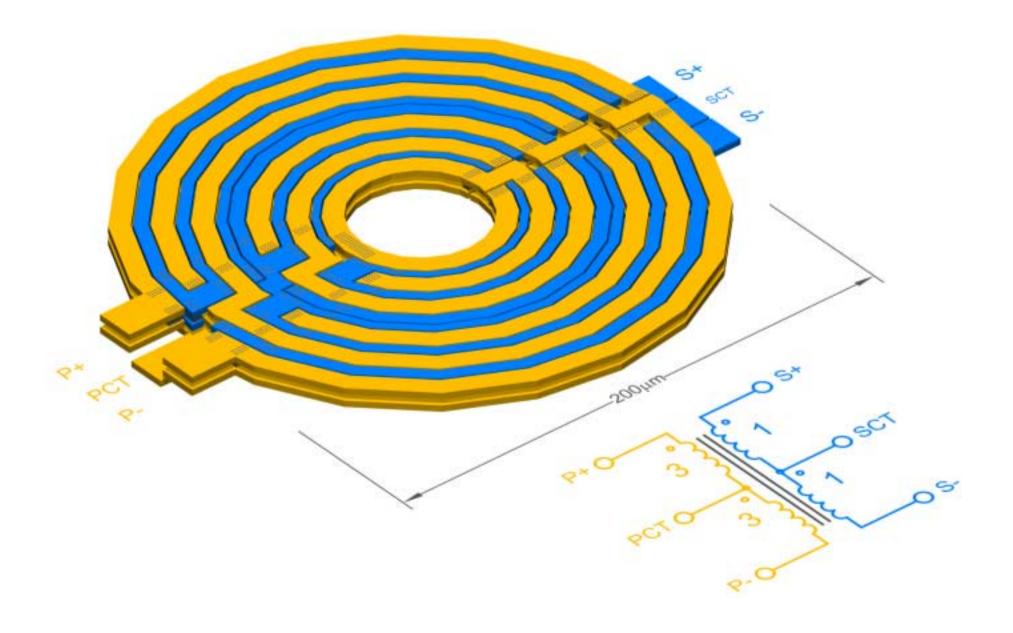

#### **2 GHz Monolithic Transformer 3-D View**

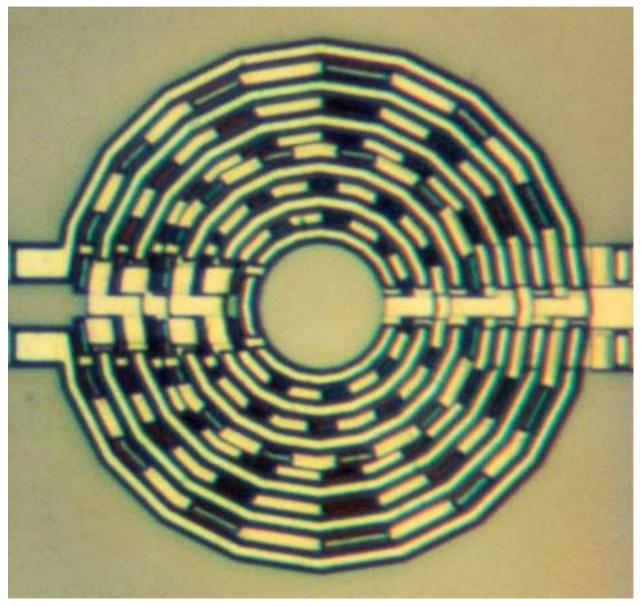

#### 2 GHz Monolithic Transformer (Ø 200 μm)

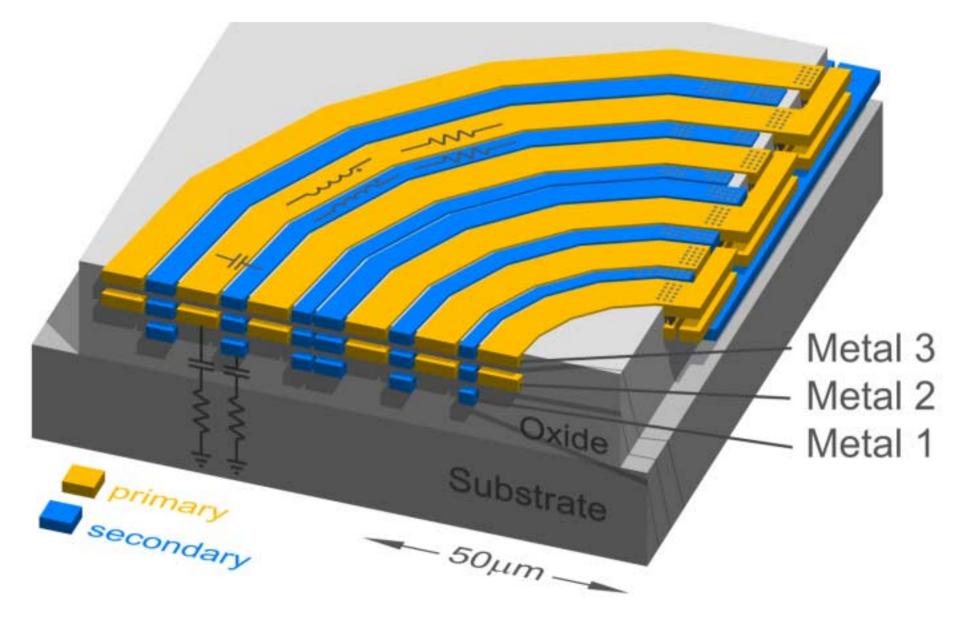

#### **Transformer Cross Section**

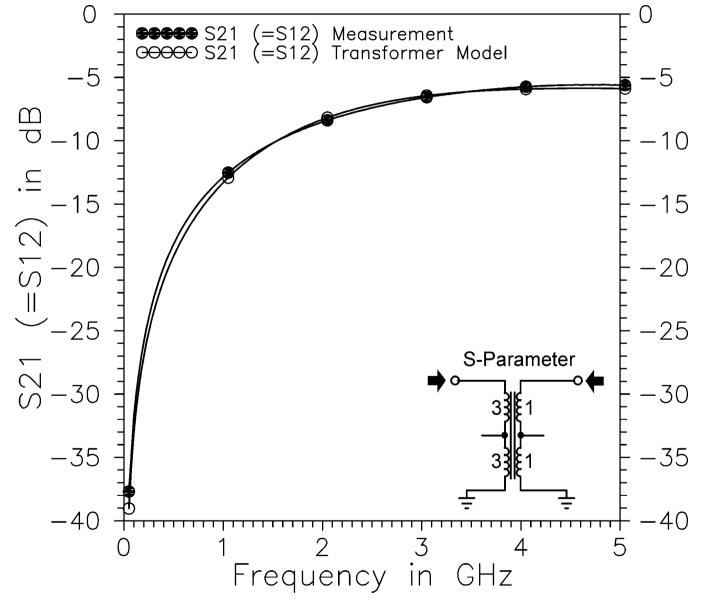

### **Transformer Transmission Coefficient**

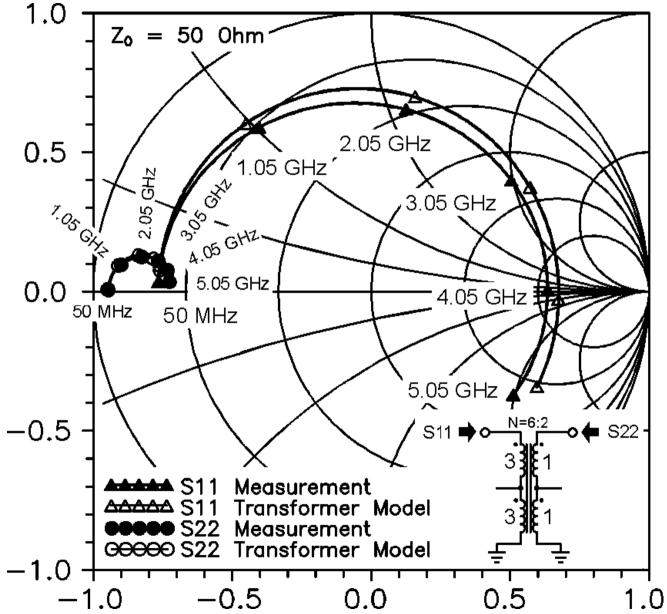

### **Transformer Reflection Coefficients**

#### **Transformer Inductance** Ц Inductance .⊆ $L_{P}(\omega) = \frac{\text{Im}(Z_{11})}{\omega}$ $L_{S}(\omega) = \frac{\text{Im}(Z_{22})}{\omega}$ Inductance (1) **eeeee** Primary: Measurement COCCO Primary: Transformer Model ▲▲▲▲ Secondary: Measurement △△△△△ Secondary: Transformer Model ()-+-----Frequency in GHz

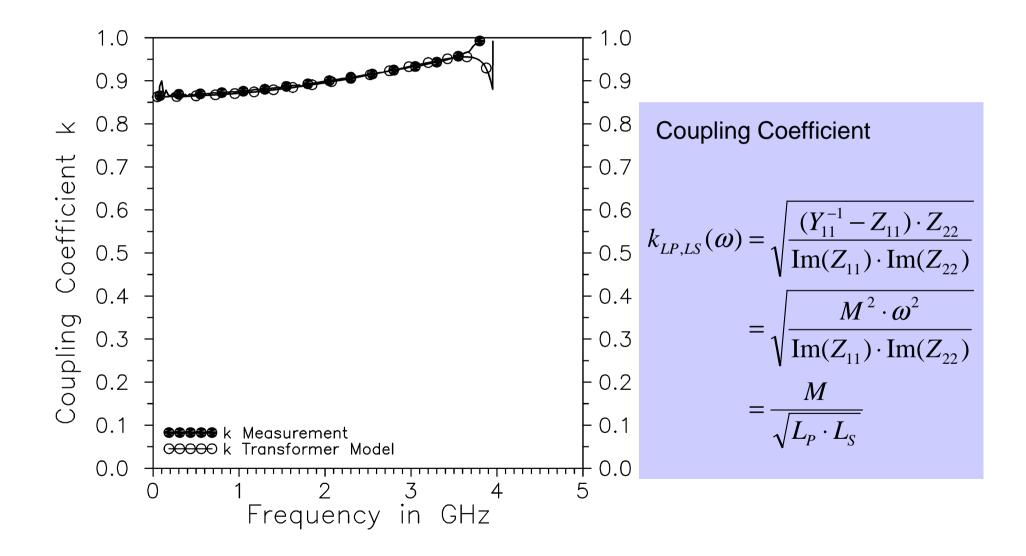

#### **Transformer Coupling Coefficient**

# Outline

#### Introduction

- ► High Performance On-Chip Transformer Design

- ► A 2.5 V, 1 W Si-bipolar PA with 55 % PAE at 1.9 GHz

- ► A 2.8 V, 3.2 W Si-bipolar PA with 54 % PAE at 900 MHz

#### ► Conclusion

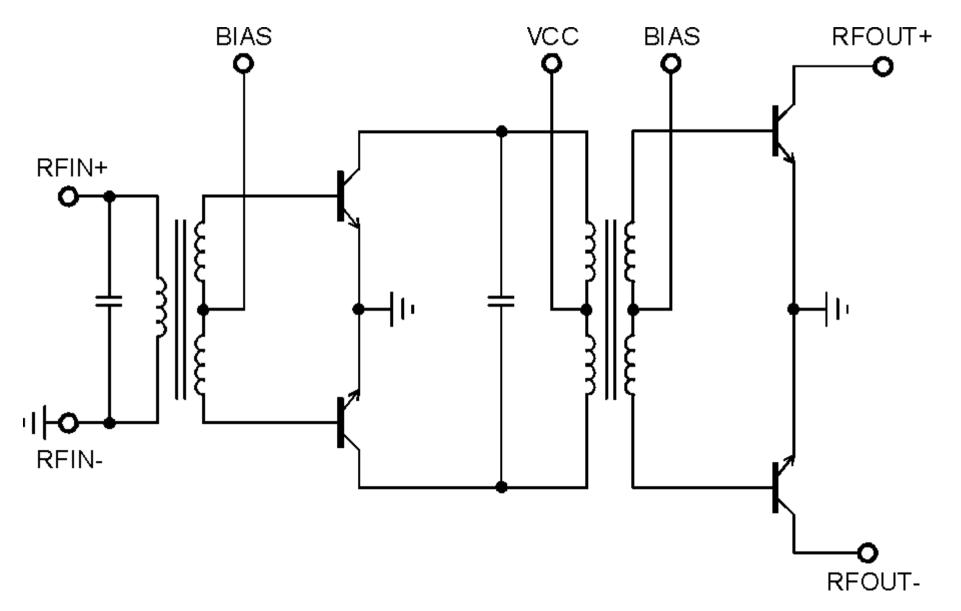

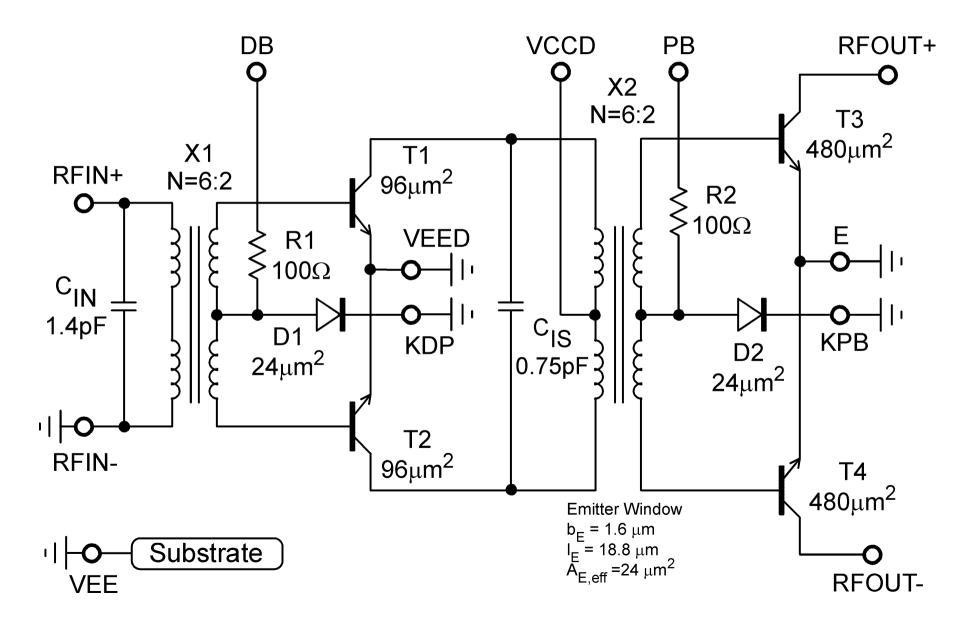

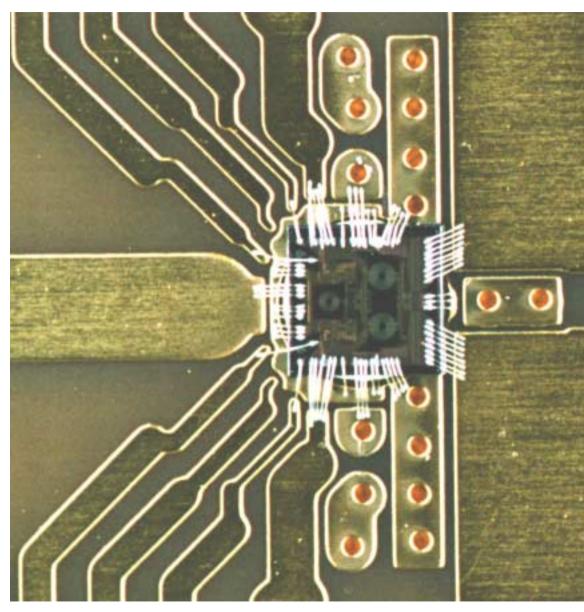

# **Circuit Diagram**

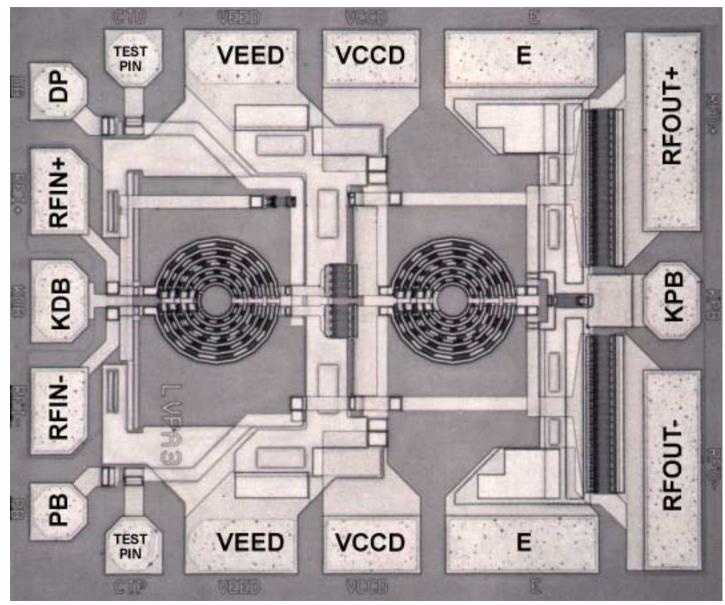

### Chip Micrograph (Size 1.17 x 0.97 mm<sup>2</sup>)

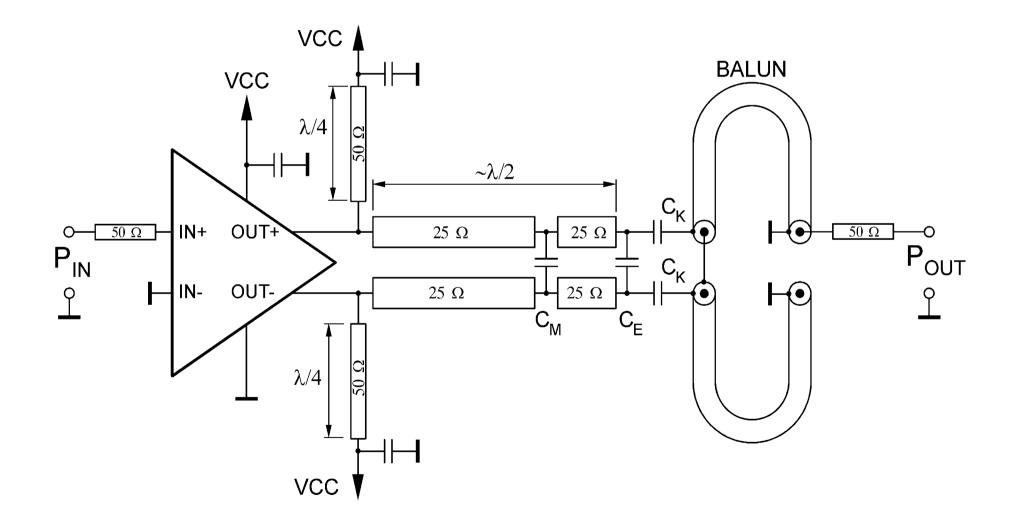

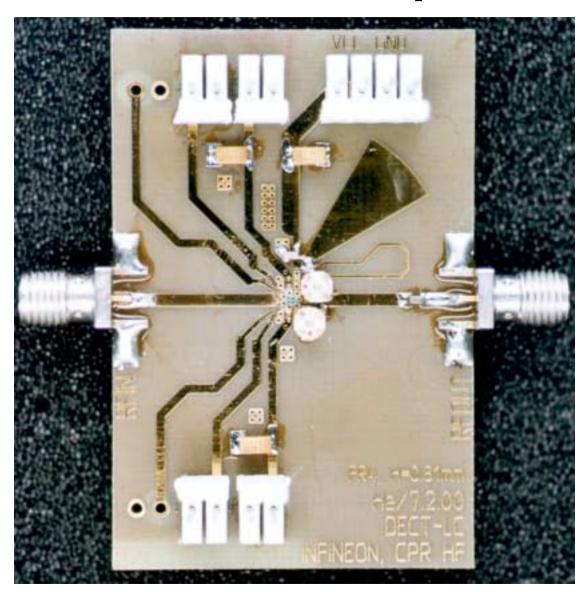

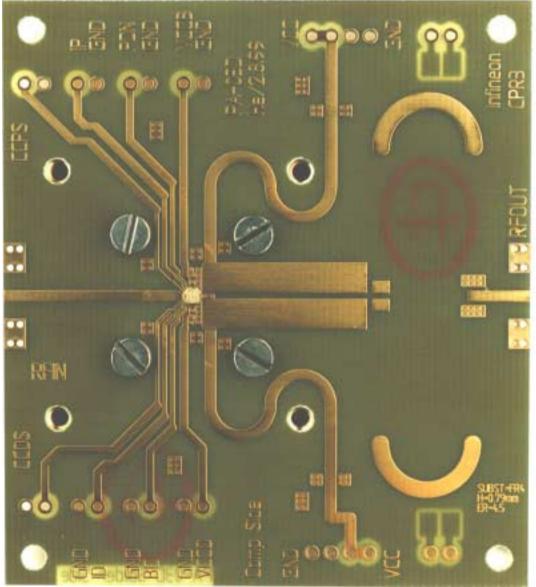

# 2 GHz Test Circuit

#### **2 GHz Test Board**

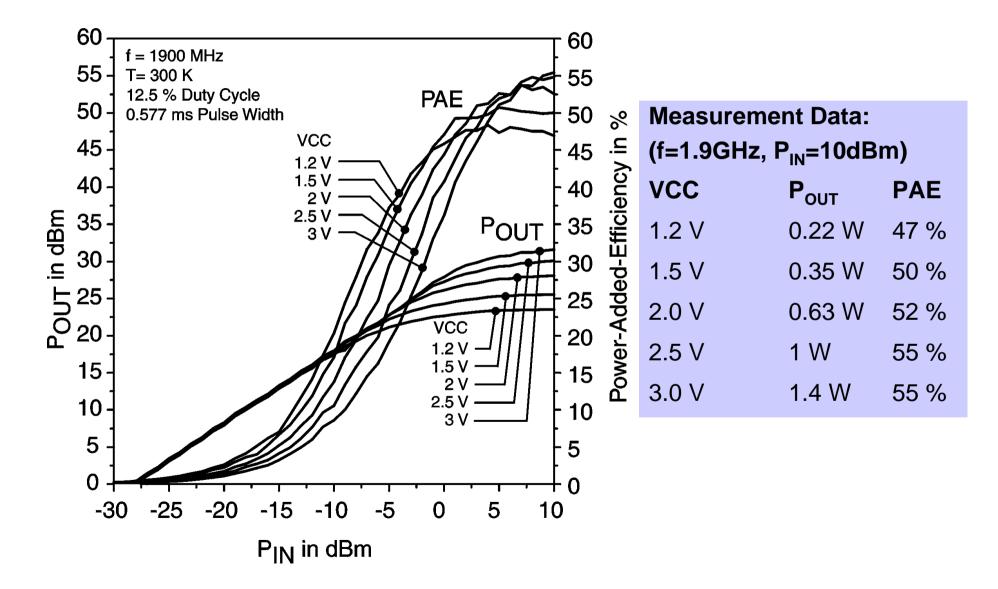

#### **Power Transfer Characteristic and PAE**

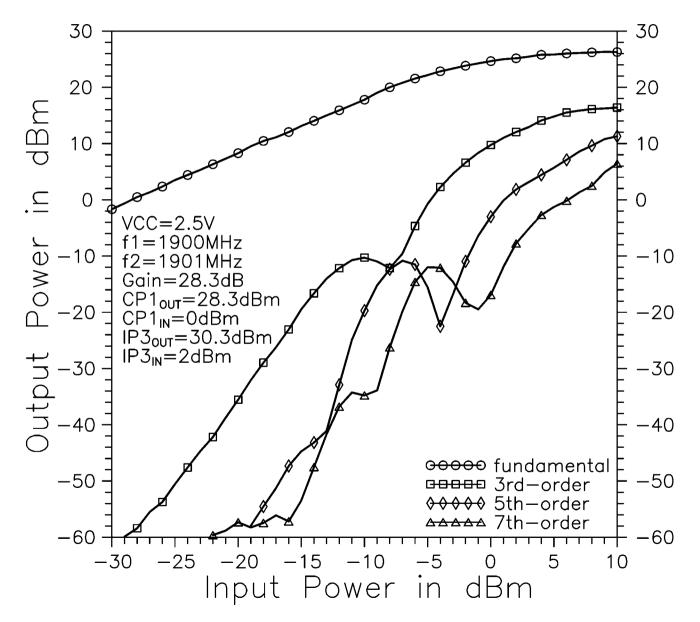

#### **Intermodulation Characteristic**

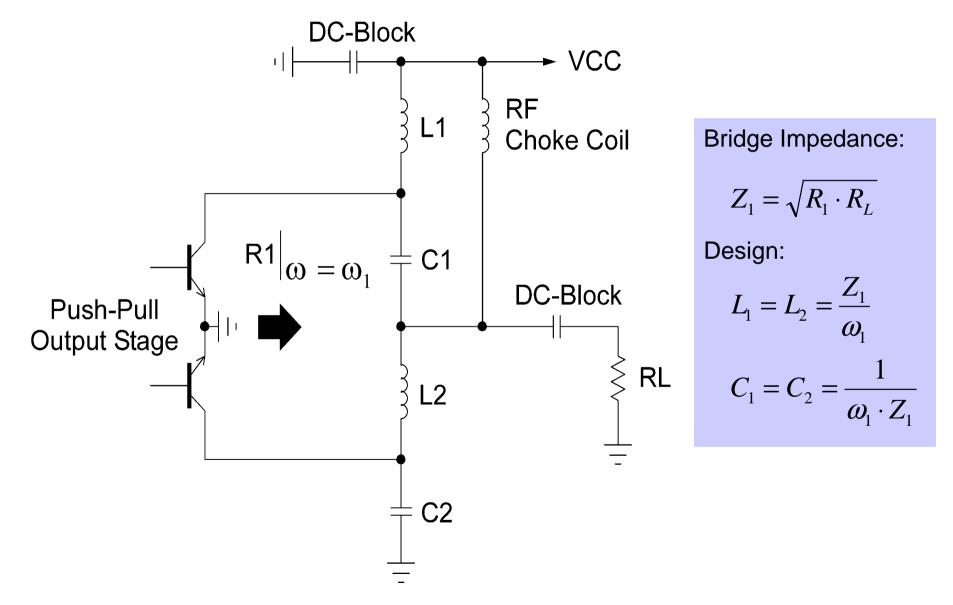

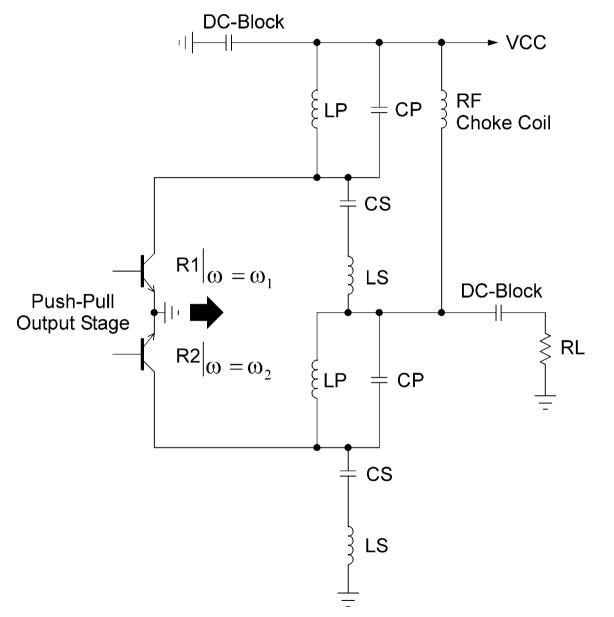

### **Application Circuit: Lumped LC-Balun**

# **Application Board: Lumped LC Balun**

## **Lumped Dual Band LC-Balun**

**Bridge Impedances:**  $Z_1 = \sqrt{R_1 \cdot R_L}$  $Z_2 = \sqrt{R_2 \cdot R_L}$ **Design:**  $L_{S} = \frac{\omega_{1} \cdot Z_{1} + \omega_{2} \cdot Z_{2}}{\omega_{2}^{2} - \omega_{1}^{2}}$  $\underline{\omega}_2 - \underline{\omega}_1$  $C_{S} = \frac{\omega_{1} \quad \omega_{2}}{\omega_{1} \cdot Z_{2} + \omega_{2} \cdot Z_{1}}$  $L_{p} = \frac{\left(\frac{\omega_{2}}{\omega_{1}} - \frac{\omega_{1}}{\omega_{2}}\right) \cdot Z_{1} \cdot Z_{2}}{\omega_{1} \cdot Z_{1} + \omega_{2} \cdot Z_{2}}$  $C_{P} = \frac{\omega_{1} \cdot Z_{2} + \omega_{2} \cdot Z_{1}}{(\omega_{2}^{2} - \omega_{1}^{2}) \cdot Z_{1} \cdot Z_{2}}$  $\omega_2 > \omega_1$

# **Performance Summary**

| Operating Frequency                                                   | 1800 - 2000                                 | MHz |

|-----------------------------------------------------------------------|---------------------------------------------|-----|

| Supply Voltage                                                        | 1.2 - 3                                     | V   |

| Maximum Output Power<br>(at 1.2 V / 3 V and 1900 MHz, Pin = 10 dBm)   | 0.22 / 1.4                                  | W   |

| Maximum PAE<br>(at 0.22 W / 1.4 W and 1900 MHz)                       | 47 / 55                                     | %   |

| Output-Stage Collector Efficiency<br>(at 0.22 W / 1.4 W and 1900 MHz) | 61 / 67                                     | %   |

| Small-signal Gain (at 1900 MHz)                                       | 28                                          | dB  |

| Technology                                                            | 0.5 μm, 50 GHz f <sub>⊤</sub><br>Si-Bipolar |     |

# Outline

- Introduction

- High Performance On-Chip Transformer Design

- ► A 2.5 V, 1 W Si-bipolar PA with 55 % PAE at 1.9 GHz

- ► A 2.8 V, 3.2 W Si-bipolar PA with 54 % PAE at 900 MHz

- ► Conclusion

#### Challenges

- Output Power > 2.5 W at 900 MHz and 2.8 V

- Efficiency > 50 %

- Power Supply Range 2.8 V to 4.5 V

- Standard 0.8  $\mu$ m Si-Bipolar Technology, f<sub>T</sub> = 25 GHz

#### **Approaches Used**

- Push-Pull Type Circuit

- 900 MHz High Performance Transformers

- Closed Loop Bias Circuit

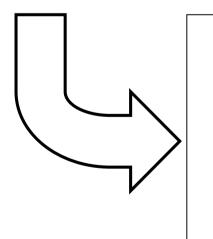

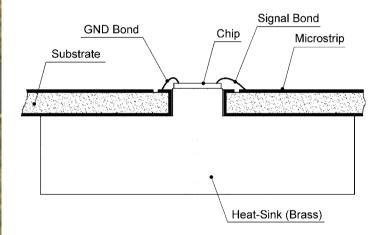

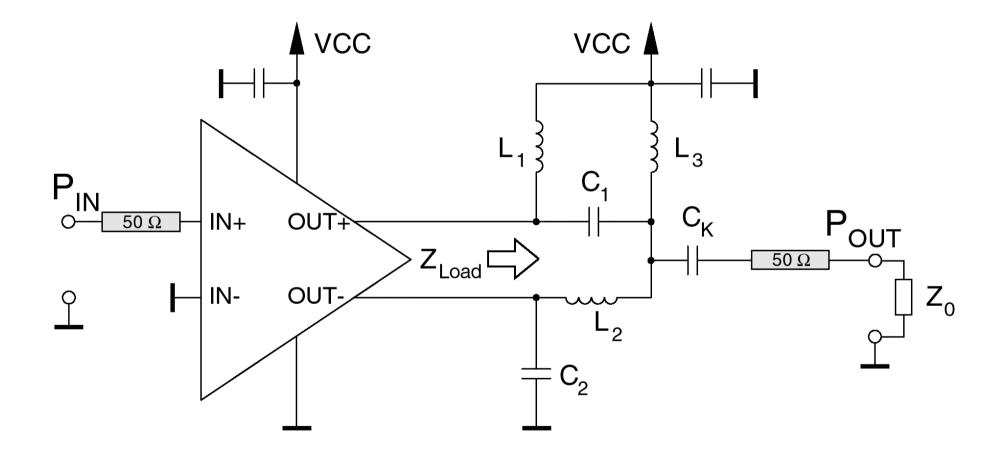

# 900 MHz PA Circuit Diagram

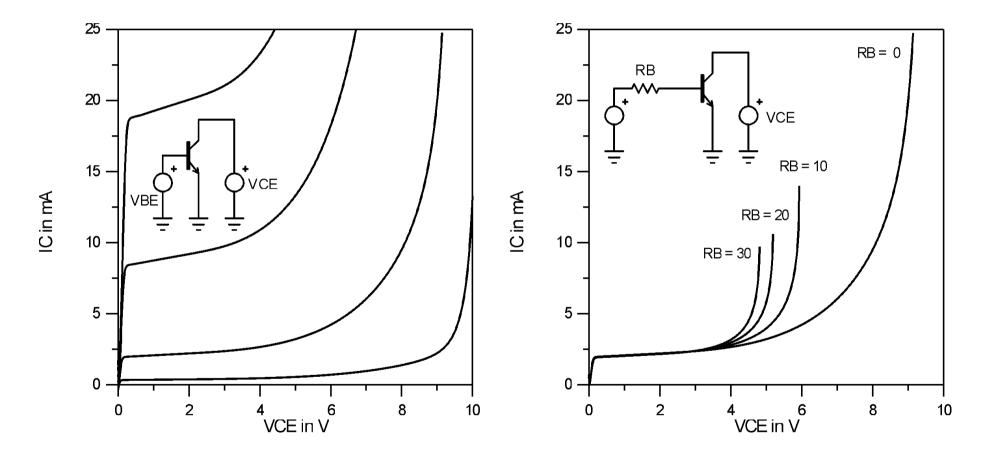

### **BJT Breakdown Characteristics**

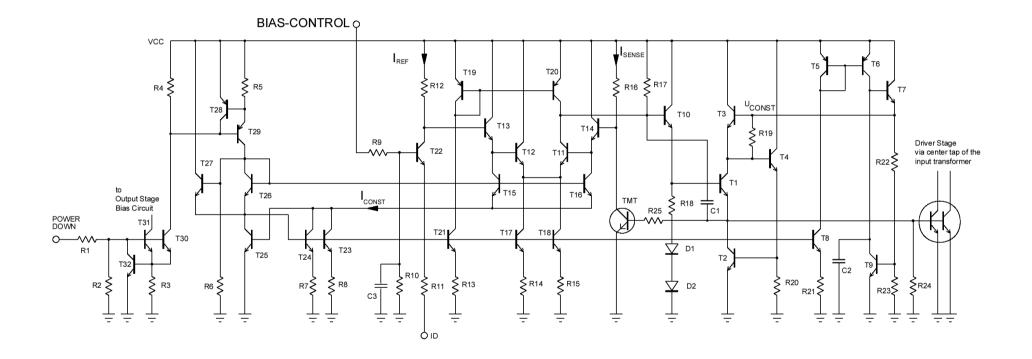

# **Bias Opamp Circuit Diagram**

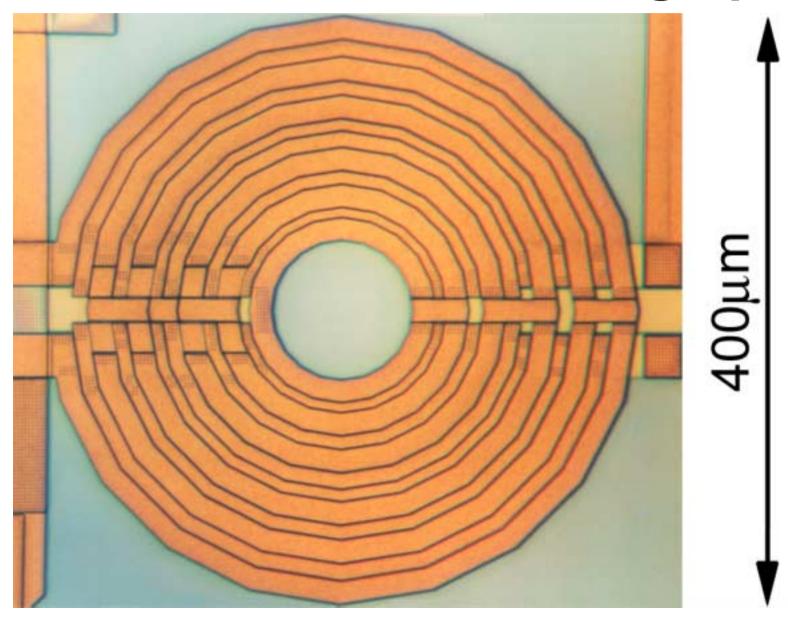

# 900 MHz Transformer Photograph

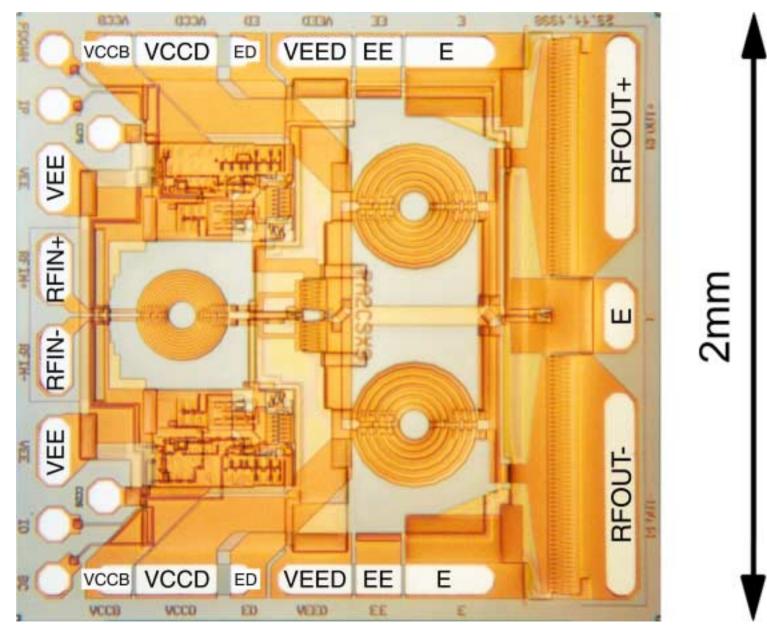

# **Chip Photograph**

# 900 MHz Test Circuit

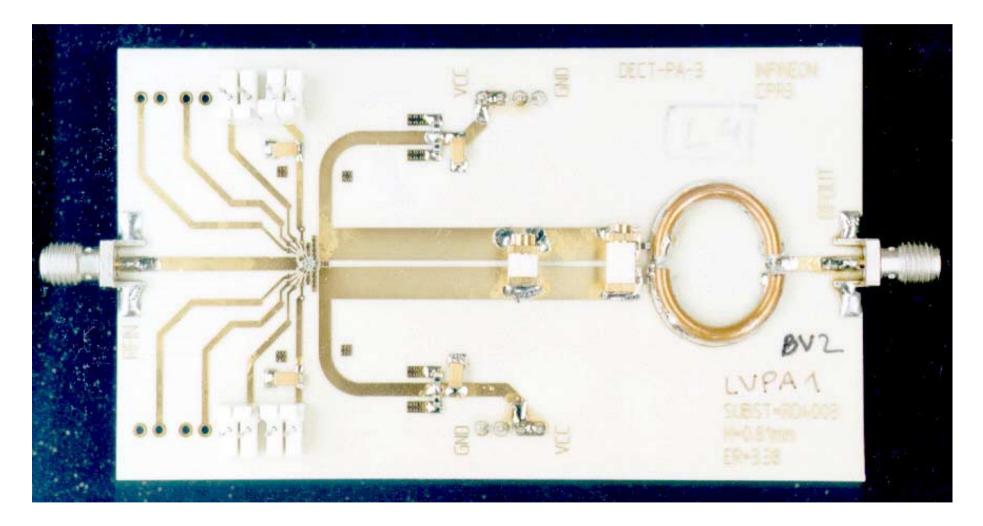

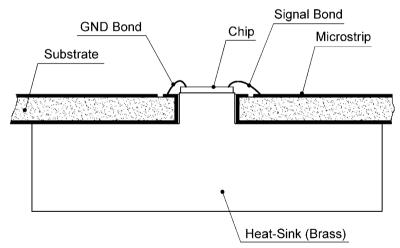

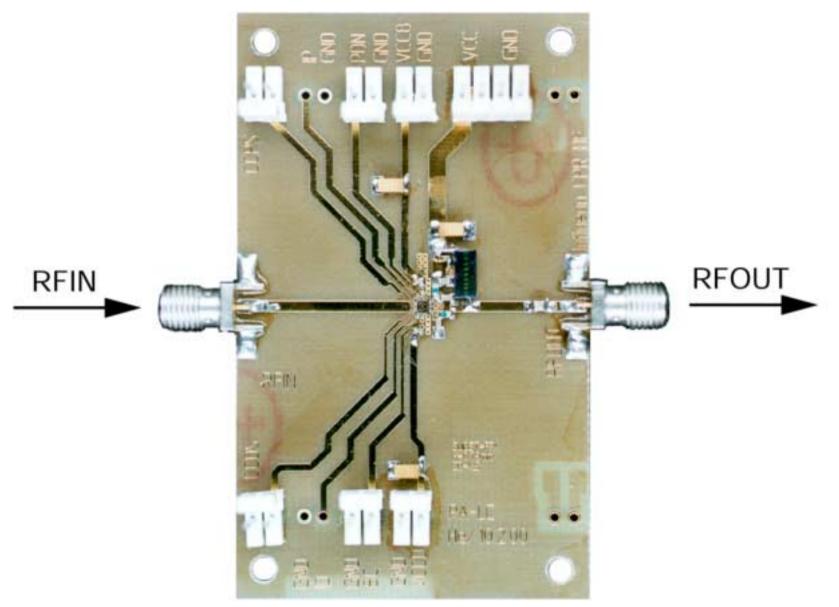

# **Power Amplifier Test Board**

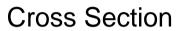

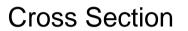

#### **Cross Section**

Power Amplifier Test Printed Circuit Board (FR4, 70 x 78 mm<sup>2</sup>)

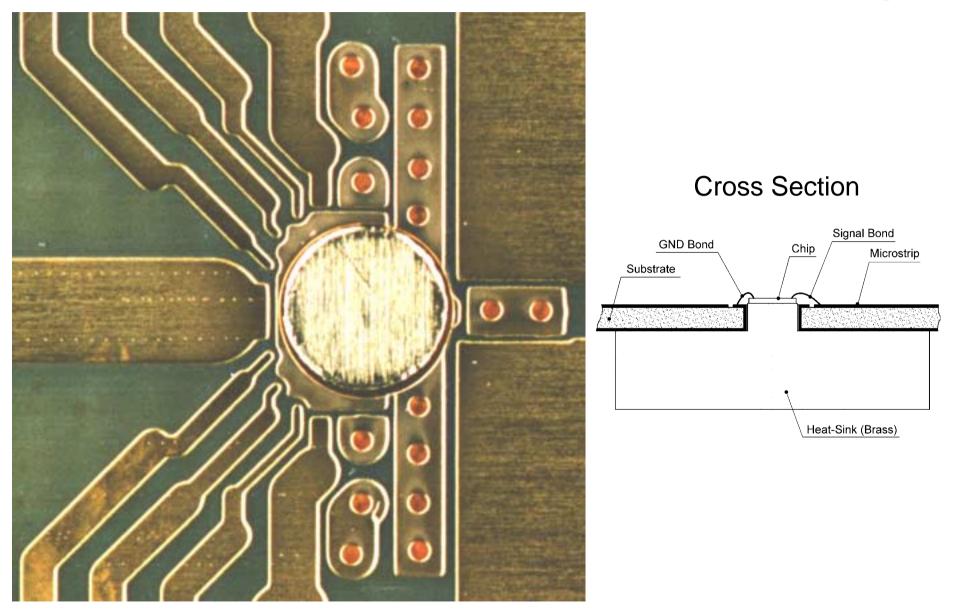

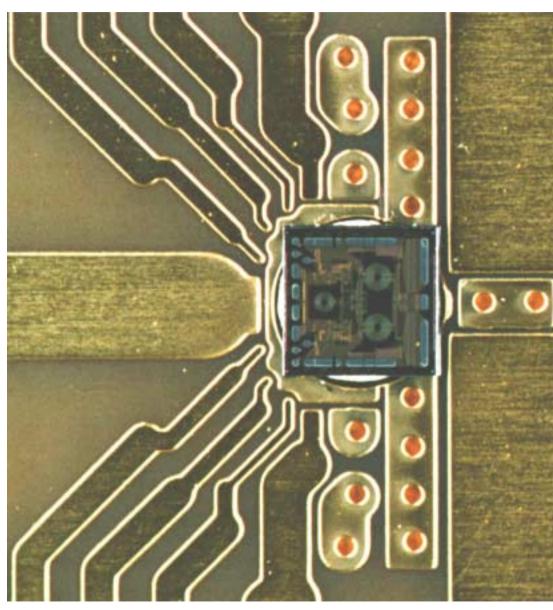

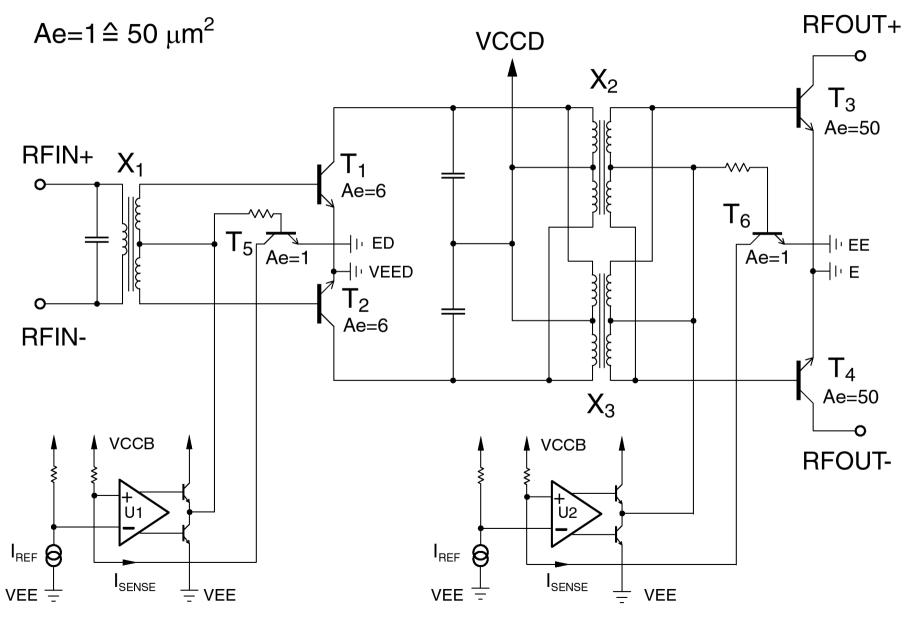

## **Test Circuit Detail View (Heat-Slug)**

## **Test Circuit Detail View (Heat-Slug)**

# 900 MHz PA Circuit Diagram

### **Test Circuit Detail View (Heat-Slug)**

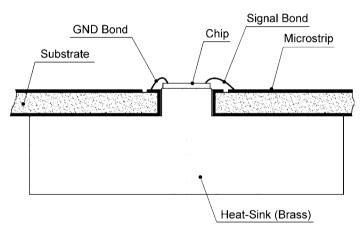

#### **Power Amplifier Test Board Top-View**

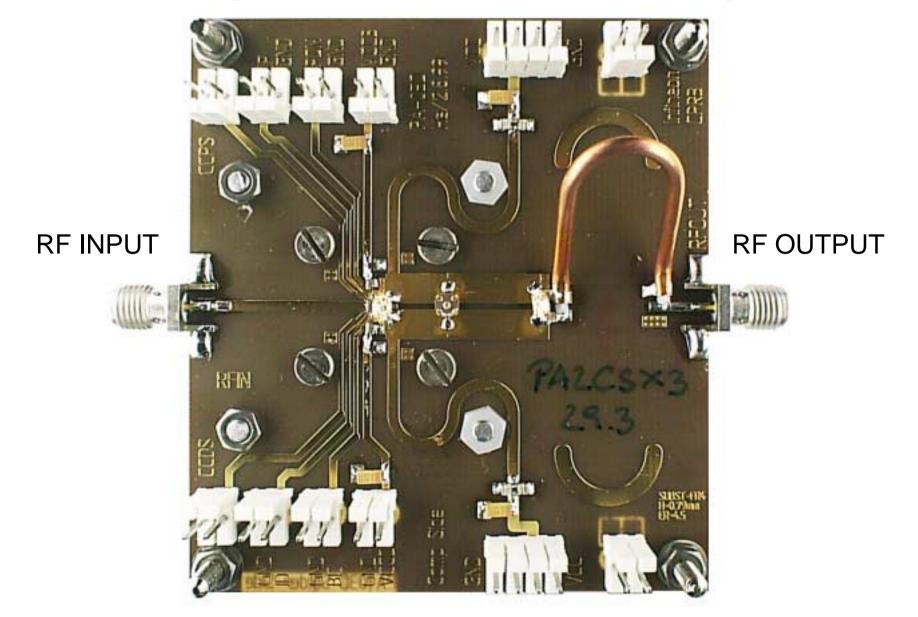

#### **Power Amplifier Test Board Bottom-View**

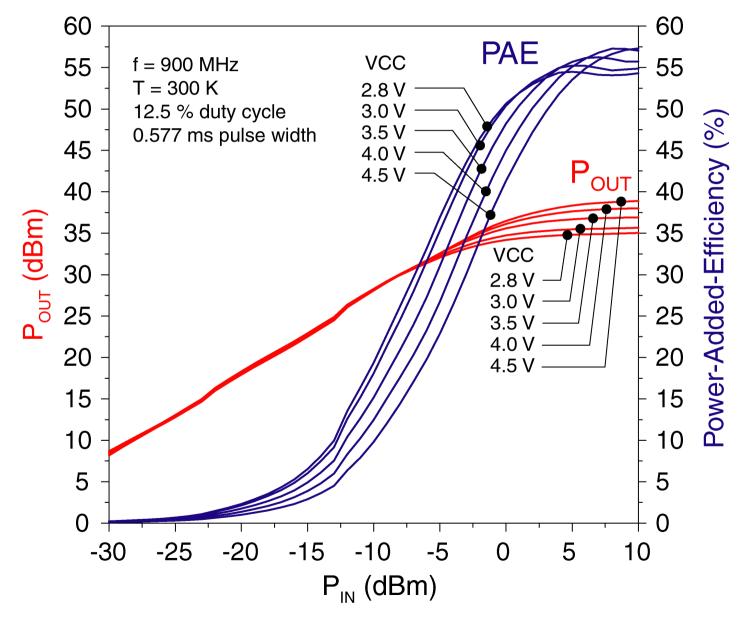

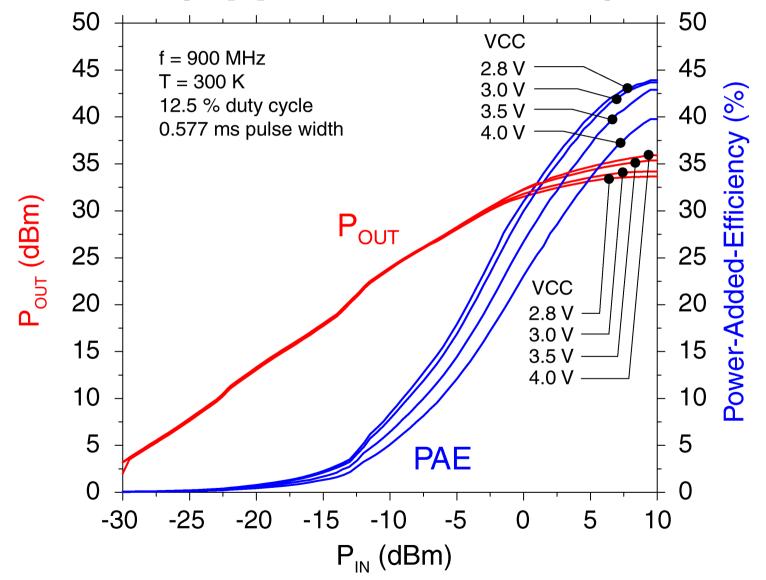

#### **Power Transfer Characteristic (Test Board)**

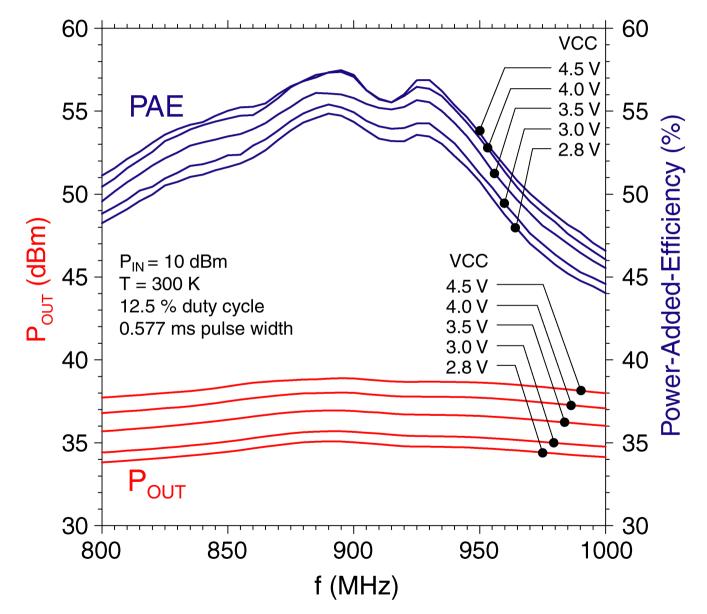

## Frequency Response (Test Board)

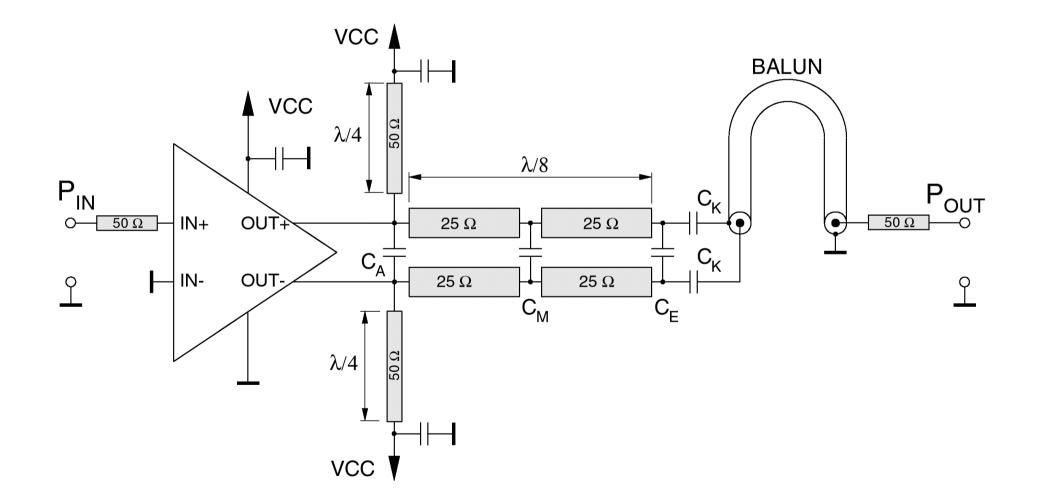

#### **Application Circuit**

## **Application Board**

#### Power Transfer Characteristic and PAE (Application Board)

# **Performance Summary**

| Operating Frequency                                                  | 800 - 1000                                  | MHz |

|----------------------------------------------------------------------|---------------------------------------------|-----|

| Supply Voltage                                                       | 2.8 - 4.5                                   | V   |

| Maximum Output Power<br>(at 2.8 V / 4.5 V and 900 MHz, Pin = 10 dBm) | 3.2 / 7.7                                   | W   |

| Maximum PAE<br>(at 3.2 W / 7.7 W and 900 MHz)                        | 54 / 57                                     | %   |

| Output-Stage Collector Efficiency<br>(at 3.2 W / 7.7 W and 900 MHz)  | 66 / 68                                     | %   |

| Input VSWR (at 900 MHz)                                              | 1.7                                         |     |

| Small-signal Gain (at 900 MHz)                                       | 38                                          | dB  |

| Technology                                                           | 0.8 µm, 25 GHz f <sub>⊤</sub><br>Si-Bipolar |     |

## Conclusion

High performance on-chip transformer

- Integrated push-pull type PAs in Si-bipolar:

- a) 1 W, 1.9 GHz, 55 % PAE at 2.5 V

- b) 3.2 W, 900 MHz, 54 % PAE at 2.8 V